|

FLIP-FLOP

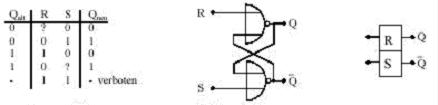

Eine sehr wichtige Klasse von Schaltnetzen sind Flip-Flops. Hierbei handelt es sich um einfache Schaltwerke mit zwei Eingängen und zwei Ausgängen, die in Abhängig-keit von den Eingängen und dem aktuellen Zustand zwei stabile Zustände annehmen können. Die einfachtse Form des Flip-Flops ist das R-S-Flip-Flop. Es kann mit NOR-Gattern folgendermaßen realisiert werden:

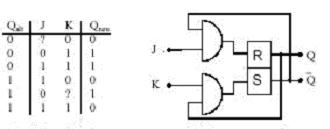

Bei einem R-S-Flip-Flop sind die Ausgänge Q und.Q immer zueinander invers, der Zustand Q =.Q ist also ausgeschlossen. Die Eingänge R (Reset) und S (Set) haben folgende Funktion: Ist S=0 und R=0, so bleibt der aktuelle Zustand des Flip-Flops un-verändert. Ist R=1 und S=0, so stellt sich der Zustand Q=0 und.Q =1 ein. Ist R=0 und S=1, so stellt sich der Zustand Q=1 und.Q =0 ein. R=1 und S=1 führt zu keinem stabi-len Zustand von Q und.Q und muss deshalb vermieden werden. Man kann leicht ausschließen, dass die nicht erlaubte Kombination R=1 und S=1 auf-treten kann, indem man eine weitere Rückkopplung einführt. Das so modifizierte Flip-Flop wird als J-K-Flip-Flop bezeichnet:

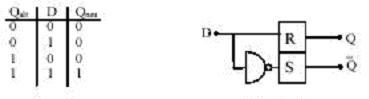

Wird jetzt J=K=1 gesetzt, so kippt das Flip-Flop in den Zustand Q ..Q,.Q . Q, denn zuvor ist ja entweder Q=1 oder.Q=1 gewesen, so dass sich nun entweder an R oder an S der Zustand 1 einstellen wird, aber niemals an R und S gleichzeitig.Fasst man die Eingänge J und K zu nur einem Eingang T zusammen, so erhält man ein T-Flip-Flop mit dem Trigger-Eingang T. Ist T=0, so behält das Flip-Flop seinen Zustand bei. Ist T=1, so kippt das Flip-Flop, d.h. es erfolgt der Übergang Q -> Q und Q -> Q.Eine weitere Variante ist das D-Flip-Flop, das als Verzögerungsglied (Delay) verwen-det werden kann. Dazu wird der S-Eingang eines R-S-Flip-Flops über einen Inverter mit dem R-Eingang verbunden. Es ist dadurch immer S =.R Gewähr leistet, so dass sich sich der Zustand an D mit einer gewissen Verzögerungszeit am Ausgang Q durchsetzt. Die Schaltung und die Übergangstabelle lauten:

Meist werden Flip-Flops mit einem zusätzlichen Eingang t, dem Takteingang, verse-hen. Man spricht dann von einem taktgesteuerten Flip-Flop. Die am Eingang anlie-gende Information wird in diesem Fall erst dann wirksam, wenn ein Taktimpuls an t erscheint. Dabei wird noch unterschieden, ob das Flip-Flop mit der steigenden Flanke, dem stabilen Zustand, oder der fallenden Flanke des Taktimpulses schaltet. Schließlich sei noch das Master-Slave-Flip-Flop erwähnt, das aus zwei hintereinan-der geschalteten, taktgesteuerten Flip-Flops besteht. Bei einem Taktimpuls übernimmt das erste Flip-Flop die anliegende neue Information, während das zweite Flip-Flop zunächst in seinem Zustand verbleibt und erst beim folgenden Taktimpuls die Information des ersten Flip-Flops übernimmt. Flip-Flops werden als Speicher (beispielsweise für Register), als Verzögerungsglieder, in Zählern und vielen anderen Anwendungen eingesetzt.Die Komponenten digitaler Rechenanlagen, beispielsweise Rechenwerk, Steuerwerk, Register und Speicher bestehen im Wesentlichen aus Schaltwerken, die daher eine zentrale Stellung in der technischen Informatik einnehmen.

|

|

|